Over the years, many manufacturers have gone forward and tried to make FPGA development easier, but they have become a blush in the history of FPGA.

Since the beginning of this year, the attention of FPGAs in the industry has rapidly increased. One reason is that it is closely related to popular applications such as artificial intelligence and VR. Another reason is that international companies such as Intel and local giants such as Ziguang Group have added to the eye of FPGAs. The acquisition financing is hot, and there is a tendency to compete with CPU and GPU. However, traditionally, FPGA development is not as simple as an X86 processor. It requires professional tools, professional knowledge, and even a chip design foundation. The main way to develop its application is to use the lowest-level hardware implementation, which is also a factor hindering its popularity.

On the one hand, FPGA has become an unstoppable trend, on the one hand its users are limited to a few hardware engineers. How to liberate FPGAs so that more applications can benefit from the flexibility and high performance of power consumption of FPGAs? This problem, in the past few years, has never been a variety of attempts to try to lower the development threshold of FPGAs, and most of them eventually become an insignificant history. In the end, I can change this history, I am afraid I still have to rely on the leading boss of Xilinx. In addition to the introduction of software-defined design environments such as SDSoC, SDAccel, SDNet, which allows software engineers to easily develop FPGA applications, it is liberating the existing limitations of FPGAs by supporting and building an eco-partner environment. Recently, its partner PLDA has developed a new process that is expected to make FPGAs truly popular.

A workflow called QuickPlay developed by PLDA claims to efficiently solve implementation complexity problems and provide multiple usage modes for FPGA development. The core of its value is that its software developers will use the application originally for the CPU, partially or fully on the FPGA hardware. QuickPlay is able to leverage the power of FPGA resources to turn these powerful and complex devices into a software-defined platform that delivers the benefits of FPGAs without the need for hard hardware design. Cow!

Anyone who has done design knows that hardware execution algorithms have great advantages in both time and power consumption. Using DSP software for image processing is not only time-consuming but also extremely power-intensive, while FPGAs are used for high efficiency. Amazing!

What kind of process is QuickPlay? Any tool designed to help software developers use their custom hardware to enhance their application should have the following characteristics:

Create functional hardware from pure software code;

Use existing hardware IP modules as needed;

Call and create all supporting hardware (interfaces, controls, clocks, etc.);

Support the use of off-the-shelf commercial development boards and custom platforms;

Ensure that the generated hardware automatically constructs corrections so that no hardware debugging is required; and that functional modules can be debugged using only standard software debugging tools.

PLDA designed QuickPlay to meet all requirements, allowing pure software developers to specify, build and integrate FPGAs into their software architecture with minimal effort.

Software-centric approach Using QuickPlay to implement the entire design process is fairly straightforward:

1. Develop a C/C++ language functional model of the hardware engine.

2. Verify the functional model using standard C/C++ language debugging tools.

3. Specify the target FPGA platform and I/O interfaces (PCIe, Ethernet, DDR, QDR, etc.).

4. Compile and build the hardware engine.

QuickPlay uses an intuitive data flow model that guarantees deterministic execution from a mathematical perspective, independent of the execution engine. The model consists of a parallel function called the kernel that is responsible for communicating with the stream channel. So it's closely tied to the software developer's outline of the application on the whiteboard. To ensure behavioral certainty, these cores must communicate with each other to prevent data conflicts such as race conditions and deadlocks. The way to achieve this is to use stream channels that have the following characteristics: (1) based on FIFO, (2) blocking and blocking writes, and (3) point-to-point.

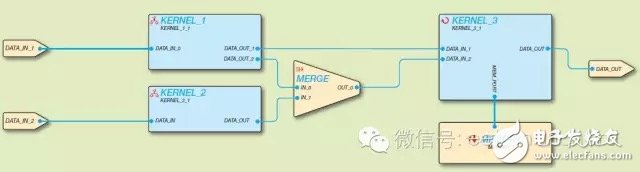

These are the characteristics of the Kahn Process Network (KPN) that PLDA relies on to build QuickPlay's computing model. The QuickPlay design example in Figure 1 describes the KPN model.

Figure 1 - Design example in QuickPlay

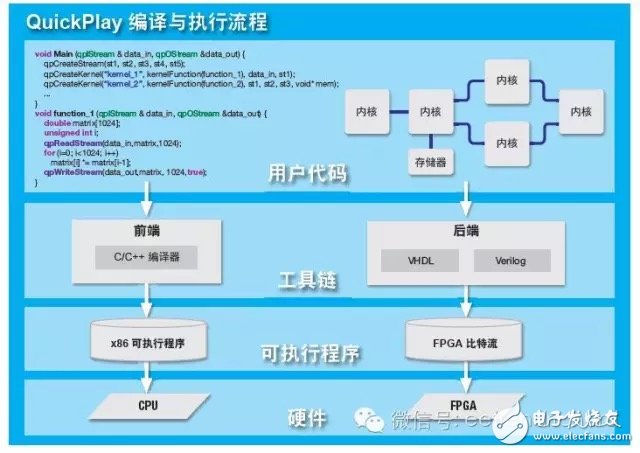

The content of any kernel can be any C/C++ language code, third-party IP, or even HDL code (for hardware designers). QuickPlay uses a fairly straightforward design process (Figure 3).

Figure 2 – QuickPlay uses a simple and intuitive design flow.

What are the benefits of QuickPlay for developers?The benefits of QuickPlay are obvious. Developers don't have to worry about what happens to kernel functions, and don't worry about the timing, clocks, communication stacks, protocols, and other similar issues that hardware engineers often encounter. As long as the constraints are obtained, there is no hardware. Level verification and debugging. This is a great tool that really makes it easy for software developers to develop FPGAs.

Industrial Switches,Gigabit Ethernet Switch,12 Port Industrial Switch,Managed Switches 8 Port

Shenzhen Scodeno Technology Co.,Ltd , https://www.scodenonet.com