At the recent Hot Chips conference held in California, Baidu unveiled its groundbreaking XPU, a 256-core cloud computing acceleration chip powered by FPGA technology. This collaboration with Xilinx marks a significant milestone in Baidu's ongoing efforts in the realm of artificial intelligence and advanced computing. During the conference, Baidu also delved into the architectural intricacies of the XPU, offering a deeper understanding of its capabilities.

Over the last few years, Baidu has demonstrated impressive progress in deep learning technologies, particularly with GPU-based solutions. However, the company is now venturing into the development of a novel processor known as the XPU.

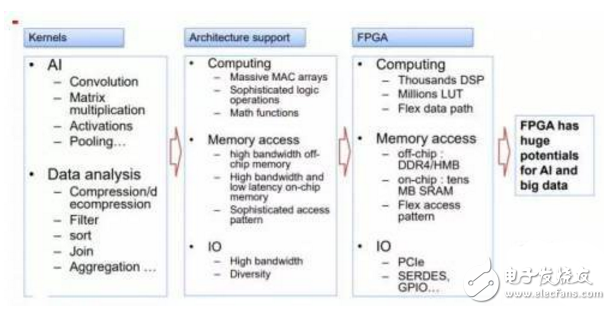

*Baidu explains the situation of AI and data analysis workloads on FPGA*

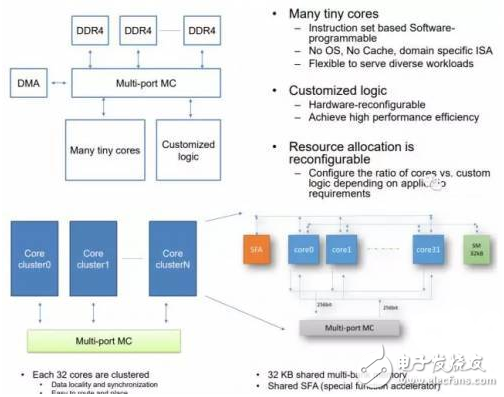

According to Baidu researcher Ouyang Jian, the XPU architecture was designed to emphasize versatility, focusing on computationally intensive, rule-based tasks while ensuring optimal efficiency, performance, and flexibility. At the Hot Chips conference, he presented the XPU alongside representatives from Xilinx, the FPGA vendor.

The primary aim of the XPU is to strike a balance between performance and efficiency while addressing diverse computational demands. While FPGAs themselves excel at handling specific tasks, their effectiveness increases significantly when multiple small cores are integrated.

Ouyang Jian noted, "FPGAs are highly efficient in executing specific computational tasks but lack programmability. Conventional CPUs are adept at general-purpose computing, especially rule-based operations, and offer great flexibility. GPUs are designed for parallel computing, thus delivering exceptional performance. The XPU focuses on compute-heavy, rule-based, and diverse computing tasks, aiming to enhance efficiency and performance while providing CPU-like flexibility."

Currently, one of the main challenges with the XPU remains its limited programmability, a common issue associated with FPGA-based systems. To date, the XPU lacks a dedicated compiler. However, Ouyang Jian mentioned that the team is actively working on developing such a tool.

Ouyang Jian further explained that to support matrix computations, convolutions, and other operations involving both large and small cores, the XPU requires a robust mathematical array with high-bandwidth, low-latency memory, along with high-bandwidth I/O interfaces. The DSP units within the FPGA provide parallel processing capabilities. Off-chip DDR4 and HBM interfaces optimize data transfer, while on-chip SRAM offers essential memory features.

In Micro Benchmark tests, the XPU demonstrates comparable efficiency to x86 cores for compute-intensive, conventional memory-access tasks. However, the XPU's scalability for data synchronization tasks needs improvement. For non-data-synchronized tasks, the XPU exhibits linear scalability relative to the number of cores.

This presents a challenge. As previously mentioned, the XPU currently lacks a compiler. This processor operates on an FPGA, receiving instructions via custom logic. These small cores resemble CPUs, meaning developers can only utilize assembly language, with all execution controlled by the host. The entire process involves dividing computational tasks, writing XPU code, and invoking specialized logic functions to compile and execute on a Linux platform.

The XPU comprises 256 cores and includes a shared memory for data synchronization. All cores operate at 600 MHz.

Ouyang Jian stated, "At Baidu, we've been utilizing FPGAs for several years now. Our data centers, cloud computing platforms, and autonomous driving projects house numerous FPGAs. Through this experience, we’ve gained insights into the strengths and limitations of FPGAs and how best to optimize them. With the XPU's large core count, we're focusing on diverse computing tasks."

Last year, certain media outlets reported on a SQL accelerator based on Baidu's deep learning SDA, which utilized the SA architecture. According to Ouyang Jian, this is also a key aspect of the XPU's memory bandwidth and latency advantages.

Ouyang Jian also showcased some benchmark tests conducted this year, though the details remain somewhat vague. Nevertheless, this marked Baidu's first public unveiling of the XPU.

If the XPU proves successful in applications related to AI, data analysis, cloud computing, and autonomous driving, Baidu might consider transitioning to ASIC technology for future iterations of the XPU.

Hybrid Light Tower

Hybrid light tower

A hybrid light tower is a type of lighting system that combines traditional lighting technologies, such as high-intensity discharge (HID) lamps, with renewable energy sources, such as solar panels and wind turbines. This combination allows the light tower to operate independently of the electrical grid, making it a more sustainable and cost-effective lighting solution.

The hybrid light tower typically consists of a tall tower structure with multiple light fixtures mounted at the top. The tower is equipped with solar panels and/or wind turbines, which generate electricity from the sun and wind. This electricity is stored in batteries or used directly to power the light fixtures.

During the day, the solar panels collect sunlight and convert it into electricity, which is stored in batteries for use during the night or in cloudy conditions. The wind turbines generate electricity when there is sufficient wind, further contributing to the power supply.

Hybrid

light tower is an advanced lighting tower, it can save 40% fuel, save maintenance,

save labor. It operates from the latest solar and battery combination, backed

up by a small fuel-efficient diesel engine. Utilizing latest, hybrid

technology, provide less consumed power than traditional towers for huge fuel

savings and reduced COâ‚‚ output.

Hybrid Light Tower,Hybrid Solar Mobile Light Tower,Hybrid Solar Light Tower,Solar Mobile Light Tower

Grandwatt Electric Corp. , https://www.grandwattelectric.com